OPOS6UL SP Interfaces description

Contents

Introduction

This article describe the bus interface communication between the i.MX6UL(L) and the spartan6. In i.MX6UL(L) the bus used to make communication with the FPGA is named EIM for External Interface Module. All description of this bus can be found under the i.MX6UL(L) reference manual in chapter 21 (page 821).

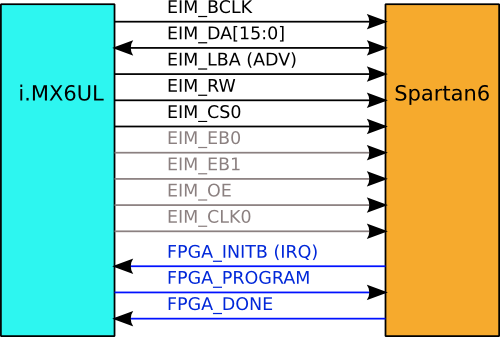

Simplified view

Normal communication between i.MX6UL(L) processor and Spartan6 fpga is done with black following signals :

- EIM_BCLK : Clock

- EIM_DA[15:0]: 16bits data and address bus

- EIM_LBA (ADV): Signal used for data/address muxing

- EIM_RW: Read/Write control signal

- EIM_CS0: Chip select

Gray following signals can be used by EIM (External Interface Memory), but not used in default configuration :

- EIM_EB0: Select byte 0 on bus

- EIM_EB1: Select byte 1 on bus

- OE : Output enable

- EIM_CLK0: second clock

Blue following signals are used for FPGA configuration from imx. Some EIM (black) signals are also used for it.

- FPGA_INITB: Initialize FPGA

- FPGA_PROGRAM : Program (configure) FPGA

- FPGA_DONE: FPGA configuration is done.

Default configuration on CSx

Clocks

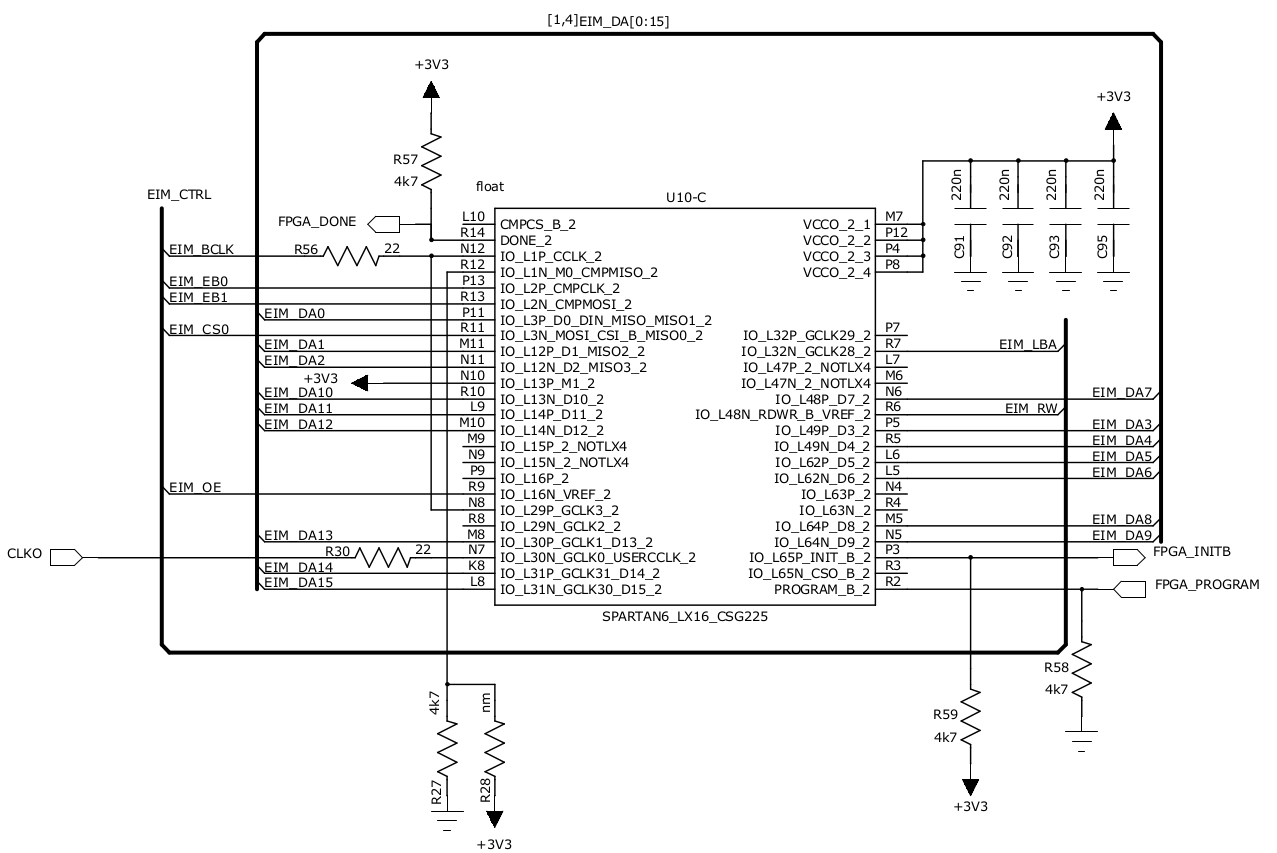

The clock used to clock the FPGA is EIM_BCLK (IO_L1P_CCLK_2(N12) and IO_L29P_GCLK3_2(N8)) and is configured to 99 MHz.

Chip Select

The EIM memory space is mapped into 128 MB total memory space in the processor memory. This memory space begin at address 0x50000000

| Start address | End address | Size | Name |

|---|---|---|---|

| 0x5000_0000 | 0x57FF_FFFF | 128 MB | EIM (NOR/SRAM) |

The total 128 MB of memory can be divided among the EIM four chip selects. See reference manual of i.MX6ULL for more information.

Timings

Read

Todo

Write

Todo

HDL register access examples

Pinout

Schematics interfaces is given here :

UCF example for interface generated by POD is given here :

NET "rstgen_syscon00_ext_clk" LOC="N8" | IOSTANDARD=LVCMOS33; # EIM_BCLK NET "rstgen_syscon00_ext_clk" TNM_NET = "rstgen_syscon00_ext_clk"; TIMESPEC "TS_rstgen_syscon00_ext_clk" = PERIOD "rstgen_syscon00_ext_clk" 10.101 ns HIGH 50 %; NET "imx6ul_wb16_wrapper00_imx_da<0>" LOC="P11" | IOSTANDARD=LVCMOS33; # EIM_DA0 NET "imx6ul_wb16_wrapper00_imx_cs_n" LOC="R11" | IOSTANDARD=LVCMOS33; # EIM_CS0 NET "imx6ul_wb16_wrapper00_imx_da<1>" LOC="M11" | IOSTANDARD=LVCMOS33; # EIM_DA1 NET "imx6ul_wb16_wrapper00_imx_da<2>" LOC="N11" | IOSTANDARD=LVCMOS33; # EIM_DA2 NET "imx6ul_wb16_wrapper00_imx_da<10>" LOC="R10" | IOSTANDARD=LVCMOS33; # EIM_DA10 NET "imx6ul_wb16_wrapper00_imx_da<11>" LOC="L9" | IOSTANDARD=LVCMOS33; # EIM_DA11 NET "imx6ul_wb16_wrapper00_imx_da<12>" LOC="M10" | IOSTANDARD=LVCMOS33; # EIM_DA12 NET "imx6ul_wb16_wrapper00_imx_da<13>" LOC="M8" | IOSTANDARD=LVCMOS33; # EIM_DA13 NET "imx6ul_wb16_wrapper00_imx_da<14>" LOC="K8" | IOSTANDARD=LVCMOS33; # EIM_DA14 NET "imx6ul_wb16_wrapper00_imx_da<15>" LOC="L8" | IOSTANDARD=LVCMOS33; # EIM_DA15 NET "imx6ul_wb16_wrapper00_imx_adv" LOC="R7" | IOSTANDARD=LVCMOS33; # EIM_LBA NET "imx6ul_wb16_wrapper00_imx_da<7>" LOC="N6" | IOSTANDARD=LVCMOS33; # EIM_DA7 NET "imx6ul_wb16_wrapper00_imx_rw" LOC="R6" | IOSTANDARD=LVCMOS33; # EIM_RW NET "imx6ul_wb16_wrapper00_imx_da<3>" LOC="P5" | IOSTANDARD=LVCMOS33; # EIM_DA3 NET "imx6ul_wb16_wrapper00_imx_da<4>" LOC="R5" | IOSTANDARD=LVCMOS33; # EIM_DA4 NET "imx6ul_wb16_wrapper00_imx_da<5>" LOC="L6" | IOSTANDARD=LVCMOS33; # EIM_DA5 NET "imx6ul_wb16_wrapper00_imx_da<6>" LOC="L5" | IOSTANDARD=LVCMOS33; # EIM_DA6 NET "imx6ul_wb16_wrapper00_imx_da<8>" LOC="M5" | IOSTANDARD=LVCMOS33; # EIM_DA8 NET "imx6ul_wb16_wrapper00_imx_da<9>" LOC="N5" | IOSTANDARD=LVCMOS33; # EIM_DA9 NET "irq_mngr00_gls_irq" LOC="P3" | IOSTANDARD=LVCMOS33; # FPGA_INITB

FPGA Interrupt

To generate an IRQ from the FPGA to the i.MX, the pin FPGA_INITB is used by default. It correspond to GPIO ?? on i.MX.

FPGA configuration protocol

Links

- i.MX6UL(L) reference manual (PDF chapter 21 page 821)

- i.MX6UL(L) Datasheet (PDF)

- Spartan6 configuration (PDF)

- Peripheral On Demand configuration files