Difference between revisions of "Orchestra"

From ArmadeusWiki

(→La bibliothèque de composants) |

m (→La bibliothèque de composants) |

||

| Line 59: | Line 59: | ||

</hdl_files> | </hdl_files> | ||

</pre> | </pre> | ||

| − | * le noeud '''generic_map''' est utilisé pour contenir la déclaration des paramètres GENERIC disponible sur l'élément TOP de l'IP si celui-ci est un fichier VHDL. | + | * le noeud '''generic_map''' est utilisé pour contenir la déclaration des paramètres GENERIC disponible sur l'élément TOP de l'IP si celui-ci est un fichier VHDL. Chaque entrée GENERIC de l'IP va être représentée par une balise '''generic''' qui va entièrement décrire la paramètre à l'aide des attributs suivants: |

| − | Chaque entrée GENERIC de l'IP va être représentée par une balise '''generic''' qui va entièrement décrire la paramètre à l'aide des attributs suivants: | + | |

** '''name''': C'est le nom du paramètre GENERIC qui doit être identique au nom utilisé dans l'IP | ** '''name''': C'est le nom du paramètre GENERIC qui doit être identique au nom utilisé dans l'IP | ||

** '''type''': C'est le type de paramètre, dans un premier temps, uniquement les types suivants sont supportés: | ** '''type''': C'est le type de paramètre, dans un premier temps, uniquement les types suivants sont supportés: | ||

Revision as of 18:28, 16 January 2007

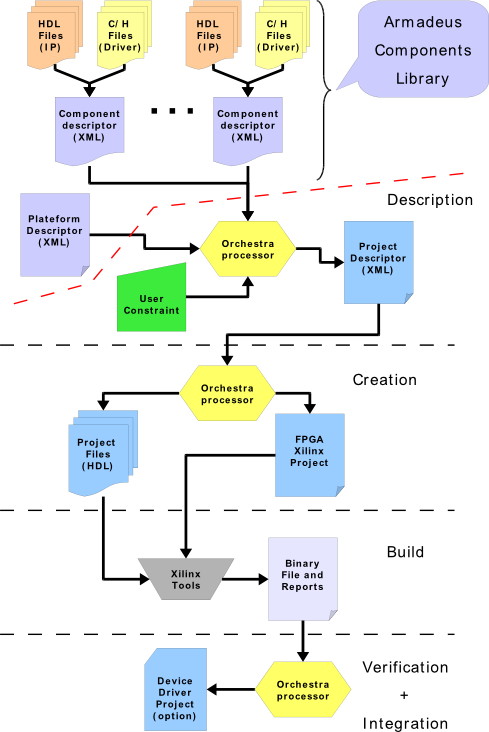

Vue d'ensemble du système Orchestra

Une image étant souvent plus explicite qu'un long texte, voici, schématiquement, le principe de fonctionnement retenu pour Orchestra.

On peut reconnaitre de ce schéma, que le système se repose sur:

- une bibliothèque de composants Armadeus Ready

- une bibliothèque de plateformes

- un projet

- une liste de fichiers modèles

A l'aide des ces composants le processeur orchestra va générer:

- un projet Xilinx complet, c'est-à-dire que l'on pourra lancer les outils Xilinx en ligne de commande avec ce projet et générer ainsi les fichiers nécessaires pour le fonctionnement du FPGA. Ce projet pourra également servir de base et être compléter par l'utilisateur pour y inclure d'autres fonctionnalités n'ayant aucun lien avec l'i.MX.

- un projet Device Driver, cette sortie est optionnelle et dépendra fortement du type de composants utilisés lors de la construction du système. En effet, ces composants devront inclure une partie driver.

La bibliothèque de composants

Un composant Armadeus Ready se compose des éléments suivants:

- un ensemble de fichiers HDL (VHDL ou Verilog)

- un ensemble de fichiers C et H (optionnel)

- un fichier XML qui va décrire entièrement le composant

Nous allons maintenant nous intéresser au contenu de ce fichier XML qui se compose de différents éléments:

- l'entête du fichier XML

<?xml version="1.0" encoding="utf-8"?>

- le noeud de base est component, il dispose des attributs suivants:

- name: le nom du composant (IP), de préférence pas plus de 16 caractères.

- version: la version du composant

- category: la catégorie dans laquelle le composant se situe. Par exemple: base, communication, etc.

<component name="irq_mngr" version="1.0" category="base"> ... </component>

Sous le noeud de base se trouve les éléments suivants:

- Le noeud description (optionnel) qui va contenir une description plus ou moins détaillée du composant. Pour ne pas limiter la saisie, les données seront placée dans une balise <![CDATA[, ainsi on pourra, par exemple, saisir des balises XML/HTML pour la mise en forme éventuelle du contenu.

<description>

<![CDATA[

The Interruption Manager is a Wishbone slave component and Armadeus compiliant.

]]>

</description>

- le noeud hdl_files va contenir la liste des fichiers VHDL ou Verilog qui composent l'IP. Chaque fichier est placé dans une base hdl_file et les attributs sont proposés:

- name: C'est le nom du fichier

- scope: Cet attribut va permettre de donner la portée du fichier, c'est-à-dire pour quel utilisation ce fichier est prévu. Voici quelques valeurs pour cet attribut:

- all: le fichier doit toujours être inclus (valeur par défaut)

- xilinx: le fichier n'est exploitable que pour des composants/outils de chez Xilinx

- Altera: le fichier n'est exploitable que pour des composants/outils de chez Altera

- tb: le fichier n'est pas synthétisable et ne fonctionne que dans le cadre de bancs de tests.

- istop: Cet attribut va permettre d'identifier le fichier TOP de l'IP. Il n'y a que 2 valeurs possible 0 (valeur par défaut) ou 1 (pour indiquer le fichier TOP).

<hdl_files> <hdl_file name="irq_mgnr.vhd" scope="all" istop="1" /> </hdl_files>

- le noeud generic_map est utilisé pour contenir la déclaration des paramètres GENERIC disponible sur l'élément TOP de l'IP si celui-ci est un fichier VHDL. Chaque entrée GENERIC de l'IP va être représentée par une balise generic qui va entièrement décrire la paramètre à l'aide des attributs suivants:

- name: C'est le nom du paramètre GENERIC qui doit être identique au nom utilisé dans l'IP

- type: C'est le type de paramètre, dans un premier temps, uniquement les types suivants sont supportés:

- integer: pour définir un nombre entier

- std_logic: pour définir un signal

- std_logic_vector: pour définir un vecteur

- valid: Cet attribut va permettre de définir la ou les valeurs ou plages de valeurs valide pour ce paramètre. Le format de ce champ n'est pas encore totalement défini, soit sous forme d'expression régulière soit sous la forme suivante:

- 1..16 ==> de 1 (inclus) à 16 (inclus)

- 8|16|32 ==> 8 ou 16 ou 32

- 1..16|32 ==> de 1 à 16 ou 32

- value: Cet attribut va permettre de définir la valeur par défaut du paramètre

<generics>

<generic name="irq_count" type="integer" value="16" valid="1..16">

<![CDATA[

irq_count gives the maximum allowed interruption sources.

]]>

</generic>

<generic name="irq_level" type="std_logic" value="1" valid="0|1">

<![CDATA[

irq_level gives the irq output signal active level.

]]>

</generic>

</generics>