Difference between revisions of "POD Tutorial 2"

m (updated pod syntax: addcomponent became addinstance) |

(→Driver generation) |

||

| Line 216: | Line 216: | ||

POD.project:uartproject.driver> copydrivers | POD.project:uartproject.driver> copydrivers | ||

</source> | </source> | ||

| + | |||

| + | == Using this POD project on target == | ||

| + | |||

| + | Now project is ready to be used on platform. To use it you have to : | ||

| + | |||

| + | * generate bitstream from [[ISE_WebPack_installation_on_Linux | ISE Webpack]]. | ||

| + | * [[Target_Software_Installation#FPGA_firmware_installation | load bitstream on fpga]]. | ||

| + | * select following drivers modules in make linux26-menuconfig : | ||

| + | ** 8250 | ||

| + | <pre class="config"> | ||

| + | Device Drivers ---> | ||

| + | Character devices ---> | ||

| + | Serial drivers ---> | ||

| + | <M> 8250/16550 and compatible serial support | ||

| + | </pre> | ||

| + | ** POD | ||

| + | <pre class="config"> | ||

| + | Device Drivers ---> | ||

| + | Armadeus specific drivers ---> | ||

| + | FPGA Drivers ---> | ||

| + | <M> Drivers generated by POD | ||

| + | </pre> | ||

| + | * [[Toolchain | compile linux and rootfs]]. | ||

| + | * [[Target_Software_Installation | flash kernel and rootfs]]. | ||

| + | * boot card. | ||

| + | * load following modules : | ||

| + | ** irq_ocore | ||

| + | ** 8250 | ||

| + | ** 16550_ocore | ||

| + | * play with your uart in ''/dev/ttyS0''. | ||

== Script == | == Script == | ||

Revision as of 09:31, 14 October 2009

Page under construction...

Informations on this page are not guaranteed !!

Informations on this page are not guaranteed !!

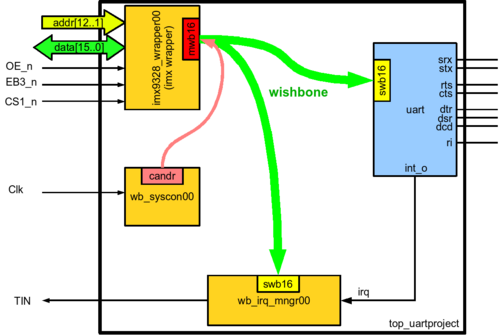

Here is a simple use case example for POD. We will create a project to include a full modem UART coming from OpenCores.org. This IP is compatible with the 16550 Linux serial driver. The platform used is the APF9328.

In this example, a complete POD project is built including the synthesis, the simulation and the generation of the Linux drivers. The operating system used to run POD is Ubuntu 7.10.

Contents

Project creation

In a terminal, run POD as follow:

$ python pod.py

POD>

The runtime file pod.py is in directory pod/bin/.

A console prompt is displayed. To create a project, enter in the project environment then write create:

POD> project

POD.project> create uartproject

Project uartproject created

POD.project:uartproject>

The project created is named uartproject. Now, the targeted platform can be selected with the selectplatform command:

POD.project:uartproject> selectplatform apf9328

Component platform added as apf9328

Component imx9328_wb16_wrapper added as imx9328_wb16_wrapper00

Component rstgen_syscon added as rstgen_syscon00

Component irq_mngr added as irq_mngr00

setting base address 0x0 for irq_mngr00.swb16

Platform apf9328 selected

POD.project:uartproject>

When the platform APF9328 is selected, POD automatically loads some components : the wrapper, the syscon and the interrupts manager corresponding to this platform. These components are used for a Wishbone bus. If they are not required they can be deleted with the delcomponent command.

To complete the project, the uart16550 component must be loaded. The component library proposes severals components categories that can be displayed with the listcomponent command:

POD.project:uartproject> listcomponents

syscons wrappers test components

UART components can be found in "components" category :

POD.project:uartproject> listcomponents components

i2cocore button irq_mngr led uart16550 ledsensor simplegpio

A component can then be load with the addcomponent command:

POD.project:uartproject> addinstance components.uart16550 uart

Component uart16550 added as uart

Now that all the components of the project are loaded, we can connect them.

Component connection

Interrupt connection

The UART component has one connection pin named interrupt.int_o, it will be connected to the irqport pin 0 of the interrupt manager (irq_mngr00):

uartproject> connectpin uart.interrupt.int_o irq_mngr00.irq.irqport.0

pin connected

FPGA connections

The UART signals must be connected outside the fpga. The platform name is used like another component of the project. The UART pins will be connected to the platform pins via the apf9328 instance.

POD.project:uartproject> connectpin uart.uart.srx_pad_i apf9328.fpga.IO_L21N_2

POD.project:uartproject> connectpin uart.uart.stx_pad_o apf9328.fpga.IO_L21P_2

POD.project:uartproject> connectpin uart.uart.rts_pad_o apf9328.fpga.IO_L22N_2

POD.project:uartproject> connectpin uart.uart.cts_pad_i apf9328.fpga.IO_L22P_2

POD.project:uartproject> connectpin uart.uart.dtr_pad_o apf9328.fpga.IO_L23N_2

POD.project:uartproject> connectpin uart.uart.dsr_pad_i apf9328.fpga.IO_L23P_2

POD.project:uartproject> connectpin uart.uart.dcd_pad_i apf9328.fpga.IO_L24N_2

POD.project:uartproject> connectpin uart.uart.ri_pad_i apf9328.fpga.IO_L40N_2

Bus connection

The irq manager was automaticaly connected to the wrapper/syscon when the platform was selected (part of the plateform), thus only the UART must be connected to the wrapper with the connectbus command:

POD.project:uartproject> connectbus imx9328_wb16_wrapper00.mwb16 uart.swb16

Bus connected

Clock connection

The Wishbone bus requires a clock and a reset connection to be assigned, this can be done by means of the addbusclock command.

> addbusclock rstgen_syscon00.candr imx9328_wb16_wrapper00.mwb16

Connected

This connection is done automatically when command autoconnectbus is called.

Code generation

The component connections are now done. The Intercon and the Top components can then be automatically generated.

Intercon

The intercon is a component creating the connections for the Wishbone bus. It is generated with the intercon command and with the master bus interface as parameter :

POD.project:uartproject> intercon imx9328_wb16_wrapper00.mwb16

setting base address 0x10 for uart.swb16

Component imx9328_wb16_wrapper00_mwb16_intercon added as

imx9328_wb16_wrapper00_mwb16_intercon

Intercon with name : imx9328_wb16_wrapper00_mwb16_intercon Done

A new component named imx9328_wb16_wrapper00_mwb16_intercon is created and added to the project.

Top

The Top component is a VHDL component creating the non Wishbone connections. To generate it just type top :

POD.project:uartproject> top

Top generated with name : top_uartproject.vhd

Toolchain project generation

The project is now fully specified, we can generate the project files for the synthesis, for the simulation and for the driver.

Synthesis

The targeted FPGA is a Xilinx Spartan3 and thus ISE is needed for the synthesis. Under the synthesis environment ISE can be selected with the selecttoolchain command :

POD.project:uartproject> synthesis

POD.project.synthesis> selecttoolchain ise

Then the synthesis project can be generated :

POD.project.synthesis> generateproject

Make directory for imx9328_wb16_wrapper

Make directory for rstgen_syscon

Make directory for irq_mngr

Make directory for uart16550

Make directory for imx9328_wb16_wrapper00_mwb16_intercon

POD.project.synthesis> generatepinout

Constraint file generated with name :

uartproject/synthesis/uartproject.ucf

POD.project.synthesis> generatetcl

Script generated with name uartproject.tcl

The generateproject command creates a subdirectory for each component and fill in it with the corresponding VHDL code. generatepinout command creates the constraint file for the fpga-pin configuration and generatetcl creates the tcl script to automatise ISE.

In ISE, to synthesize the project we just have to launch :

% source uartproject.tcl

Simulation project

TBD

Driver generation

To generate the driver, the operating system must be selected :

POD.project:uartproject> driver

POD.project.driver> selectoperatingsystem linux

Then command generateproject can be used to create the driver project:

POD.project.driver> generateproject

No driver for imx9328_wb16_wrapper

No driver for rstgen_syscon

Copy drivers template for irq_mngr

Copy drivers template for uart16550

No driver for imx9328_wb16_wrapper00_mwb16_intercon

For each component in the project, POD looks for a template driver according to the OS selected (here Linux). If a template is found, the files are copied in the project/drivers/ directory. In this example, only the irq_mngr and the uart16550 have a linux driver.

Once the template sources copied, they can be filled in with the filltemplates command :

POD.project.driver> filltemplates

Fill template for irq_mngr

Fill template for uart16550

The drivers will be copied in the Armadeus project tree with the command copydrivers. But before, the driver directory must be selected with the selectprojecttree command:

...> selectprojecttree ~/armadeus/target/linux/modules/fpga/POD

POD.project:uartproject.driver> copydrivers

Using this POD project on target

Now project is ready to be used on platform. To use it you have to :

- generate bitstream from ISE Webpack.

- load bitstream on fpga.

- select following drivers modules in make linux26-menuconfig :

- 8250

Device Drivers --->

Character devices --->

Serial drivers --->

<M> 8250/16550 and compatible serial support

- POD

Device Drivers --->

Armadeus specific drivers --->

FPGA Drivers --->

<M> Drivers generated by POD

- compile linux and rootfs.

- flash kernel and rootfs.

- boot card.

- load following modules :

- irq_ocore

- 8250

- 16550_ocore

- play with your uart in /dev/ttyS0.

Script

Scripts can be used to automatize the conception of a project. A script is a simple text file with one command per line. The # symbol can be used for delimiting comments.

Scripts can be launched directly from the command line when calling POD:

$ python pod.py scriptname

Or can be loaded from POD :

POD> source scriptname

Finally a command history can be saved as a script with the savehistory command :

POD> savehistory uartscript

The whole script for the uart project example can be found below :

project.create uartproject

project.selectplatform apf9328

project.listcomponents

project.listcomponents components

project.addcomponent components.uart16550 uart

project.connectpin uart.interrupt.int_o irq_mngr00.irq.irqport.0

project.connectpin uart.uart.srx_pad_i apf9328.fpga.IO_L21N_2

project.connectpin uart.uart.stx_pad_o apf9328.fpga.IO_L21P_2

project.connectpin uart.uart.rts_pad_o apf9328.fpga.IO_L22N_2

project.connectpin uart.uart.cts_pad_i apf9328.fpga.IO_L22P_2

project.connectpin uart.uart.dtr_pad_o apf9328.fpga.IO_L23N_2

project.connectpin uart.uart.dsr_pad_i apf9328.fpga.IO_L23P_2

project.connectpin uart.uart.dcd_pad_i apf9328.fpga.IO_L24N_2

project.connectpin uart.uart.ri_pad_i apf9328.fpga.IO_L40N_2

project.connectbus imx9328_wb16_wrapper00.mwb16 uart.swb16

project.addbusclock rstgen_syscon00.candr imx9328_wb16_wrapper00.mwb16

project.intercon imx9328_wb16_wrapper00.mwb16

project.codegen.intercon imx9328_wb16_wrapper00.mwb16

project.codegen.top

project.synthesis.selecttoolchain ise

project.synthesis.generateproject

project.synthesis.generatepinout

project.synthesis.generatetcl

project.simulation.selecttoolchain ghdl

project.simulation.generatetestbench

project.simulation.generatemakefile

project.driver.selectoperatingsystem linux

project.driver.generateproject

project.driver.filltemplates

project.driver.selectprojecttree ~/armadeus/target/linux/modules/fpga/POD

project.driver.copydrivers