Difference between revisions of "FPGA"

(→FPGA on APF9328) |

(→Links) |

||

| Line 73: | Line 73: | ||

[[Image:FrenchFlag.png]] [[Fr:FPGA|Cette page en français]] | [[Image:FrenchFlag.png]] [[Fr:FPGA|Cette page en français]] | ||

| + | |||

| + | [[Category: FPGA]] | ||

Revision as of 00:08, 28 March 2008

Contents

FPGA on APF9328

The APF9328 is equipped with a Xilinx Spartan-3 FPGA (Field Programmable Gate Array). A FPGA is a configurable digital device. Today, large and complex digital circuits and processor cores can fit into FPGAs. To find more informations about FPGAs, check the Wikipedia article

The FPGA on the APF9328 is connected to the i.MXL processor busses (data & address) and to the APF9328 connectors. This makes it possible to design your own peripherals and to put them into the FPGA. Because the FPGA can be reconfigured at any time, it allows you to replace these peripherals (or a part of them) in-situ (if other functionalities are needed, for ex). This is even possible at run-time!

FPGA Firmware Development

Digital Hardware Design

FPGAs are quite complex digital devices. Modern tools allow to describe the circuits to be implemented an abstract way, which makes it possible to manage the complexity. The trend for new tools is toward higher levels of abstraction in order to be able to manage even more complex devices in future. Nevertheless, at least basic knowledge of digital circuits and gates is necessary to start designing firmware for FPGAs.

FPGA Design-Flow

The starting point for the implementation flow is a description of the functionality in a Hardware Description Language (HDL). One of the most commonly used HDLs is VHDL (Very High Speed Integrated Circuit Hardware Description Language). VHDL files are plain text files and editing can be done in any editor.

This VHDL circuit description can be simulated to verify the functionality.

If everything is working fine, a tool called synthesizer is used to translate this HDL description in a hardware netlist. Then this netlist is mapped onto the FPGA technology. After Place and Route and Bitstream generation, a configuration file for the FPGA is created (bitfile).

For more informations about VHDL and the design flow, see [1]. This page also contains many examples that show how to describe simple electronic circuits in VHDL.

Armadeus Firmware Development Environment

Development Software

Synthesis

For FPGA development, you need the Xilinx ISE WebPack from Xilinx. It can be downloaded for free (after registration) from the Xilinx homepage [2]. The WebPack contains all you need to implement a design for the FPGA on the APF9328: Editor, Synthesizer, Mapper, Place and Route Tool, Bitstream generator, and the tools to download a configuration to the FPGA. ISE WebPack is available for Windows and Linux. See the ISE WebPack installation on Linux page for more infos.

Simulation

For simulation, Xilinx offers a free version of ModelSim, called ModelSim Xilinx Edition (MXE). It can also be downloaded from the Xilinx homepage [3] for free, but registration is required in order to receive a license. MXE is available for Windows only. The alternative for Linux users is GHDL. More information can be found on the VHDL for Linux page.

VHDL code editor

The editor in ISE is not very useful and inconvenient. In principle, any alternative editor can be used with ISE, but some have special support for VHDL-Code as syntax highlighting, template insertion, indenting and many other cool features that help to write nice and error-free code in less time. The VHDL Mode for the well known GNU Emacs editor can be recommended in particular. Emacs is available for all important operating systems.

Design Implementation

Implement your design with the ISE WebPack software. If you are new to VHDL, the information on [4] can give you a first idea. Tutorials for the ISE software can be downloaded from the Xilinx homepage [5].

Bitstream generation

When your design is ready and passes the simulation, you can create a bitstream file that can be downloaded to the FPGA. It contains all the data to configure the FPGA.

In the ISE Project Manager, make sure that a Binary Configuration File is also created. You can set this option in the properties dialog of the Generate Programming file process. Activate the option Create Binary Configuration File.

The file with the ending .bin is now the file you need to configure the FPGA on the Armadeus module.

Licence

The firmware for the FPGA has to be licenced under LGPL and BSD.

Please add to each created file a header containing the name of the "company" here it is an association, the maintainer name, the licence.

If a part of a work of an other developper has been reused, please indicate where this part has been found, the author name and keep the original licence. If no licence is specified, assume it is unlicenced.

FPGA configuration from the iMX board

Configuring the FPGA from U-Boot

See the InstallTargetSoftware page of this wiki.

Configuring the FPGA from Linux

See the FPGA loader page FPGA loader of this wiki for details.

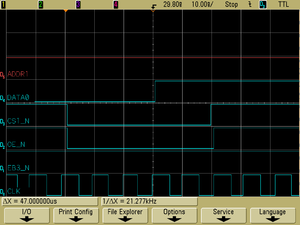

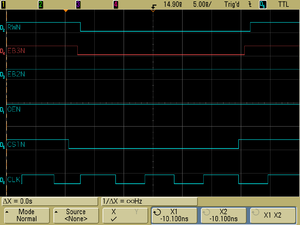

FPGA timing diagrams

The following timings diagrams have been taken with an Armadeus release 2.1