A simple design with Wishbone bus

This article intended to explain how to design Wishbone compatible components with simple example. The VHDL design can be found in sourceforge tree.

Description of wishbone structure for armadeus can be found here in french.

Contents

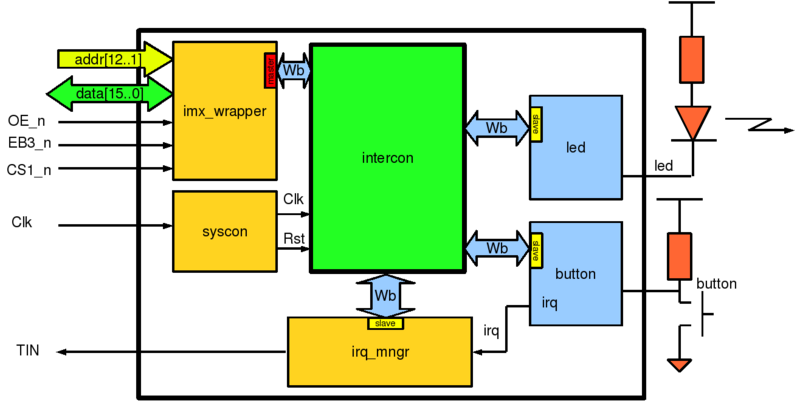

General structure

The main functionality of this component is to do the same things that benoît project : switch on a led when a button is pressed.

But to learn about designing Wishbone component and linux driver, the design is little bit more complicated (!).

When button is pressed, the component Wb_button send interrupt signal to irq_mngr. irq_mngr will toggle a flag and send interruption to i.mx processor. A Linux driver on i.mx will read irq_mngr and acknowledge irq by writing '1' on a register. And finally, Linux driver will toggle led value by writing on led register.

imx_wrapper, syscon and irq_mngr are standards

ARMadeus-Wishbone IPs that just been instantiated in our design.

Wb_button and Wb_led are simple slave component we want to integrate in the FPGA.

All these components are connected together with the 'glue logic' component intercon.

Wishbone slave application components

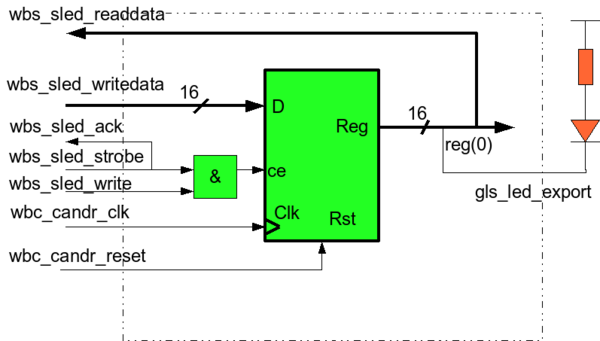

Wb_led

This component is a simple 16-bit Wishbone slave output port, from wishbone specification example (p110).

It is a simple register, that can be read and write. The led is controled with register pin 0.

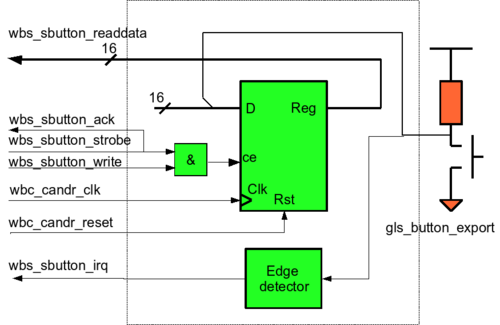

Wb_button

Wb_button component, is like Wb_led but in read only and with an edge detector to rise irq.

Drivers

Wb_led

The Wb_led driver implements a character device with read(), write() system calls. It implements sys/led/status entry. Driver sources can be found in sourceforge.

Wb_button

The Wb_button driver implements a character device with only read() system calls. If used as blocking read, it will return value only when button is push/release. Drivers sources are on sourceforge.